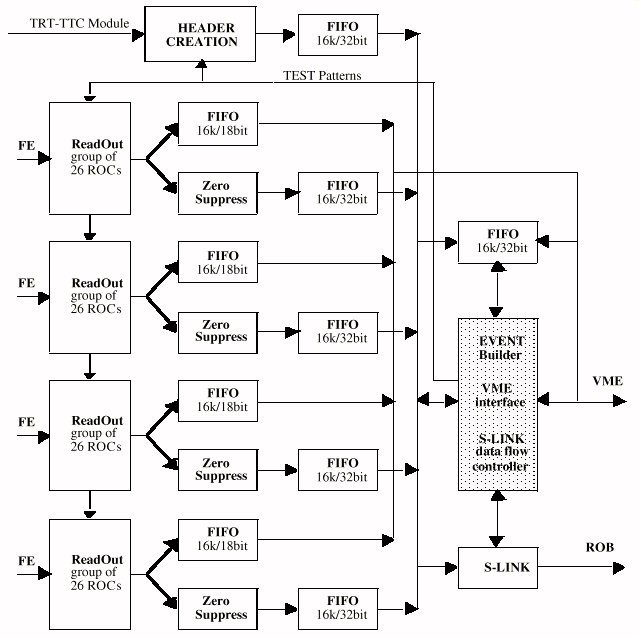

The top level block scheme of the ATLAS TRT Read Out Driver is shown in the figure. Links from ROCs are connected to the readout part (RD), outputs from RDs are connected to Zero suppresion (ZS) circuitry and buffer.

Clock and data are received from Trigger module through Trigger Module

Interface. The header of the event is generated at the Header Generate

part using headers from ROCs and data from Trigger Interface. There is

another buffering after ZS to be able to verify data before and after ZS.

The complete event is fed to the S-LINK.

| 17 November 1997 | Schematics designed. PCB design will start in December 1997. First a lightweight version of the design (without header generation and S-LINK) will be built and tested. |

| 23 April 1998 | Lightweight version testing started. Design of full version with S-LINK will start in July 1998 |

| 26 August 1998 | Prototype mini-ROD without S-LINK working. Version with S-LINK expected by middle of 1999 |

| 19 March 1999 | Design review of S-LINK part will be done beginning of May |

| 20 February 2000 | Design delayed. S-LINK will be put on front-panel, not on a transition module |

CERN - High Speed Interconnect

- S-LINK

Erik van der Bij - 14 November

2000